Debugging today's digital systems is tougher than ever. Increased product requirements, complex software, and innovative hardware technologies make it difficult to meet your time-to-market goals. The 16700 Series logic analysis systems provide the simplicity and power you need to conquer complex systems by combining state/timing analysis, oscilloscopes, pattern generators, post-processing tool sets, and emulation in one integrated system.

Agilent Technologies Innovating the HP Way

# **Table of Contents**

| System Overview                              |          |

|----------------------------------------------|----------|

| Modular Design                               | page 3   |

| Features and Benefits                        | page 4   |

| Selecting the Right System                   | page 6   |

| Mainframes                                   |          |

| Display                                      | page 7   |

| Back Panel                                   | page 8   |

| System Screens                               | page 9   |

| BenchLink XL                                 | page 12  |

| Probing Solutions                            |          |

| Criteria for Selection                       | page 13  |

| Technologies                                 | page 14  |

| Data Acquisition and Stimulus                |          |

| State/Timing Modules                         | page 16  |

| Oscilloscope Modules                         | page 75  |

| Pattern Generation Modules                   | page 28  |

| Emulation Modules                            | page 32  |

| Post-Processing and Analysis Tool Sets       |          |

| Software Tool Sets                           | page 34  |

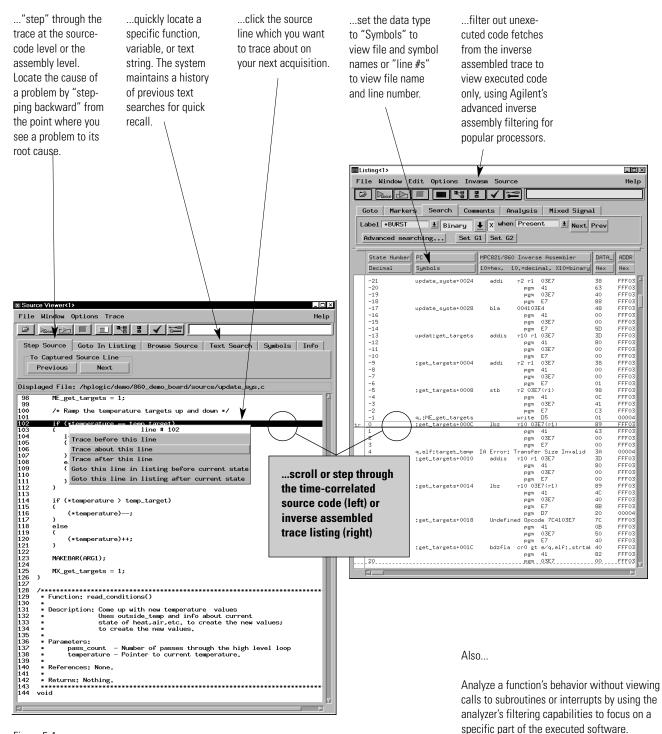

| Source Correlation                           | page 36  |

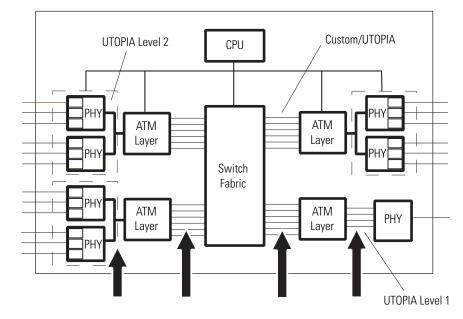

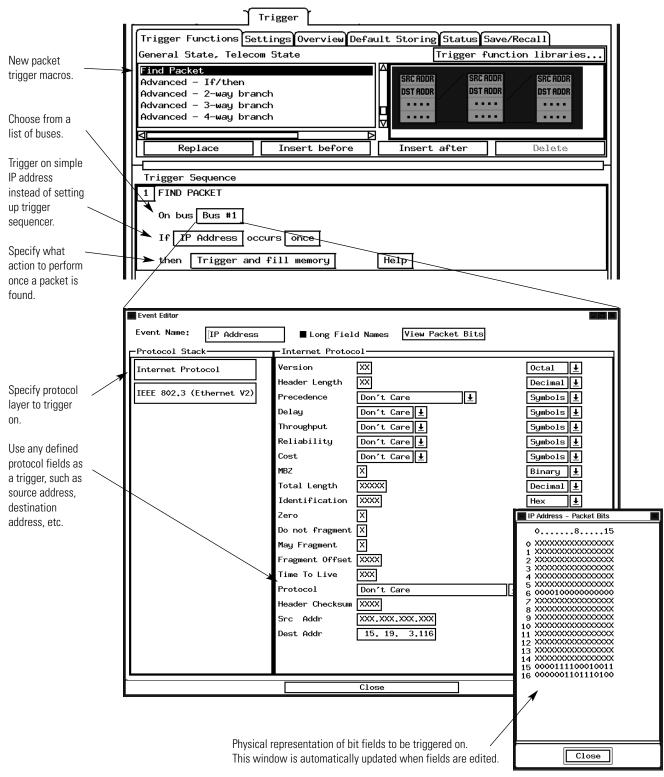

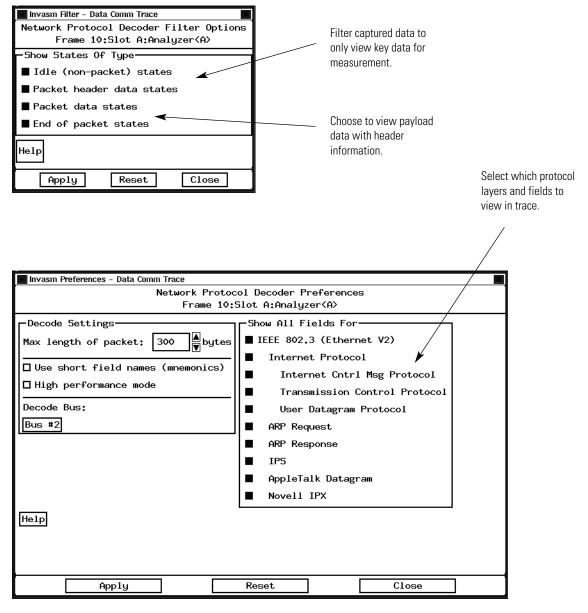

| Data Communications                          | page 40  |

| System Performance Analysis                  | page 49  |

| Serial Analysis                              | page 56  |

| Tool Development Kit                         | page 62  |

| Licensing Information                        | page 68  |

| Technical Specifications and Characteristics |          |

| Mainframe                                    | page 69  |

| Probing Solutions                            | page 77  |

| State/Timing Modules                         | page 79  |

| Oscilloscope Modules                         | page 91  |

| Pattern Generation Modules                   | page 94  |

| Trade-In, Trade-Up                           | page 103 |

| Ordering Information                         | page 104 |

| Third-Party Solutions                        | page 110 |

| Support, Warranty and Related Literature     | page 111 |

| Sales Offices Information                    | page 112 |

|                                              |          |

### **System Overview Modular Design**

#### **Modular Design Protects Your Long-Term Investment**

Modularity is the key to the Agilent 16700 Series logic analysis systems' long term value. You purchase only the capability you need now, then expand as your needs evolve. All modules are tightly integrated to provide time-correlated, cross-domain measurements.

| User Benefits<br>Agilent offers a wide variety of state/timing modules for a range<br>of applications, from high-speed glitch capture to multi-channel<br>bus analysis.                                                                      |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                                                              |  |  |

| Identify signal integrity issues and characterize signals quickly with automatic measurements of rise time, voltage, pulse width, and frequency.                                                                                             |  |  |

| Use stimulus to substitute for missing system components or to provide a stimulus-response test environment.                                                                                                                                 |  |  |

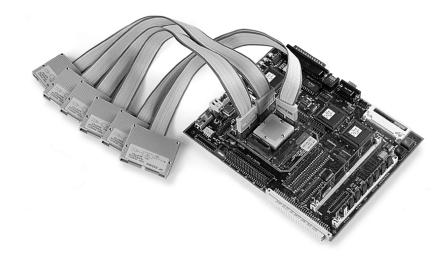

| An emulation module connects to the debug port (BDM or JTAG)<br>on your target. You have full access to processor execution<br>control features of the module through the built-in emulation<br>control interface or a third-party debugger. |  |  |

|                                                                                                                                                                                                                                              |  |  |

| Use the target control port to force a reset of your target or activate a target interrupt.                                                                                                                                                  |  |  |

| A BNC connector allows you to trigger or arm external devices<br>or to receive signals that can be used to arm acquisition<br>modules within your logic analyzer.                                                                            |  |  |

|                                                                                                                                                                                                                                              |  |  |

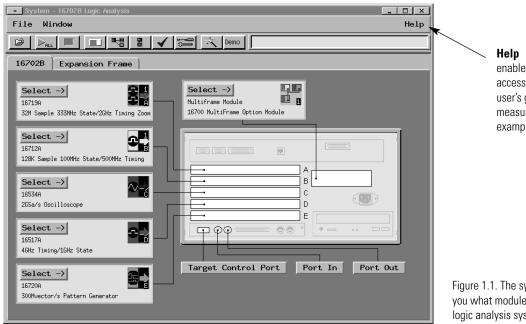

enables you to access the online user's guide and measurement examples.

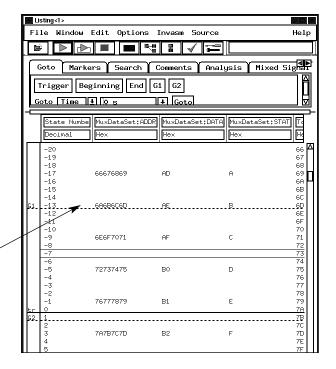

Figure 1.1. The system boot up screen shows you what modules are configured into your logic analysis system.

### **System Overview** Features and Benefits

#### System Capability

| NEW Touch Screen Interface                                                                                                           | The Agilent 16702B mainframe supports a large, 12.1 inch LCD touch screen and redesigned front panel<br>controls for an easy-to-operate, self-contained unit requiring minimal bench space and offering simple<br>portability.                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NEW Multiframe Configuration                                                                                                         | By connecting up to eight mainframes and expanders you can simultaneously view time-correlated traces for all buses in a large channel count, multibus system.                                                                                                                    |

| NEW Enhanced Mainframe Hardware                                                                                                      | Mainframe now includes a 40X CD-ROM drive, a 9 GB hard disk drive, 100BaseT-X LAN, and 128 MB of internal system RAM (optional 256 MB total).                                                                                                                                     |

| Scalable System<br>• State/timing analyzers<br>• High-speed timing<br>• Oscilloscopes<br>• Pattern generators<br>• Emulation modules | <ul> <li>Select the optimum combination of performance, features, and price that you need for your specific application today, with the flexibility to add to your system as your measurement needs change.</li> <li>View system activity from signals to source code.</li> </ul> |

#### **Measurement Modules/Interfaces**

| <b>NEW</b> The Agilent 16750A, 16751A, and 16752A State/Timing Modules          | With up to 400 MHz state speed and up to 32 MBytes of trace depth these modules help you address today's high-performance measurement requirements. (See page 18)                                                                                                                                                                                                                                                                                                                         |  |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>NEW</b> The Agilent 16720A<br>Pattern Generator                              | With up to 16 MVectors depth and 300 MVectors/sec operation and up to 240 channels[1] of stimulus, the 16720A provides a new level of capability that makes complex device substitution a reality. Supports TTL, CMOS, 3.3V, 3-state, ECL, PECL, and LVPECL.                                                                                                                                                                                                                              |  |

| NEW High-Speed Bus Measurements<br>Made Simple with Eye Finder<br>Technology    | Agilent's eye finder technology automatically adjusts the setup and hold on every channel, eliminating the need for manual adjustment and ensuring accurate state measurements on high-speed buses.                                                                                                                                                                                                                                                                                       |  |

| Timing Zoom Technology                                                          | Simultaneously acquire data at up to 2 GHz timing and 400 MHz state through the same connection. Timing Zoom is available across all channels, all the time. (See page 22)                                                                                                                                                                                                                                                                                                                |  |

| VisiTrigger Technology                                                          | <ul> <li>Use graphical views and sentence-like structure to help you define a trace event.</li> <li>Select trigger functions as individual trigger conditions or as building blocks to easily customize a trigger for your specific task.</li> </ul>                                                                                                                                                                                                                                      |  |

| Processor and Bus Support                                                       | <ul> <li>Get control over your microprocessor's internal and external data.</li> <li>Quickly and reliably connect to the device under test. (See page 32)</li> </ul>                                                                                                                                                                                                                                                                                                                      |  |

| Direct Links to Industry Standard<br>Debuggers and High-Level<br>Language Tools | <ul> <li>Debuggers provide visibility into software execution for systems running software written in C and C++ as well as active microprocessor execution control (run control).</li> <li>Import symbol files created by your language tool. Symbols allow you to set up trigger conditions and review waveform and state listings in easily recognized terms that relate directly to the names used for signals on your target and the functions and variables in your code.</li> </ul> |  |

| Direct Links to EDA Tools                                                       | <ul> <li>Use captured logic analysis waveforms to generate simulation test vectors.</li> <li>Easily find problems by comparing captured waveforms with simulated waveforms.</li> </ul>                                                                                                                                                                                                                                                                                                    |  |

[1] 240 channel system consists of five 16720A pattern generator modules with 48 channels per module. Full channel mode runs at 180 MVectors/s and 8 MVectors depth. 300 MVectors/s and 16 MVectors depth are offered in half channel mode.

# **System Overview** Features and Benefits

#### Data Transfer, Documentation, and Remote Programming

| Direct Link to Microsoft® Excel via<br>Agilent BenchLink XL 16700                           | <ul> <li>Automatically move your data from the logic analyzer into Microsoft Excel with just a click of the mouse.<br/>(See page 12)</li> <li>Use Microsoft Excel's powerful functions to post-process captured trace data to get the insight you need.</li> </ul>                                                                  |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transfer Data for Offline Analysis -<br>Data Export                                         | <ul> <li>Fast binary (compressed binary) from the FileOut tool provides highest performance transfer rate.</li> <li>ASCII format provides same format as listing display, including inverse-assembled data.</li> </ul>                                                                                                              |

| Transparent File System Access                                                              | Access, transfer, and archive files.                                                                                                                                                                                                                                                                                                |

|                                                                                             | <ul> <li>Stay synchronized with your source code by mapping shared directories and file systems from your Windows 95/98/NT-based PC directly onto the logic analyzer and vice versa.</li> <li>Move data files to and from the logic analyzer for archiving or use elsewhere.</li> </ul>                                             |

| Documentation Capability                                                                    | Save graphics in standard TIFF, PCX, and EPS formats.                                                                                                                                                                                                                                                                               |

|                                                                                             | <ul> <li>Print screen shots and trace listings to a local or networked printer.</li> </ul>                                                                                                                                                                                                                                          |

|                                                                                             | • Save your lab notes and trace data in the same file by entering relevant information in the Comments tab of the display.                                                                                                                                                                                                          |

| Remote Programming with<br>Microsoft's COM Using<br>Microsoft Visual Basic or<br>Visual C++ | <ul> <li>Perform pass/fail analysis, stimulus response tests, data acquisition for offline analysis, and system verification and characterization tests.</li> <li>Powerful-yet-efficient command set focuses on your programming tasks, resulting in a shorter learning curve while maintaining necessary functionality.</li> </ul> |

#### System Software Features

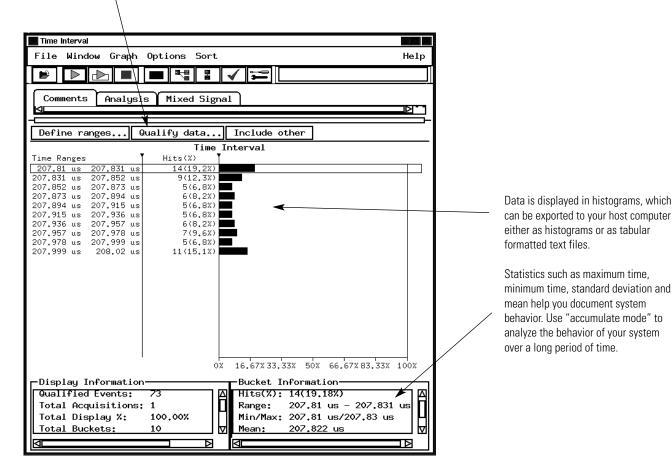

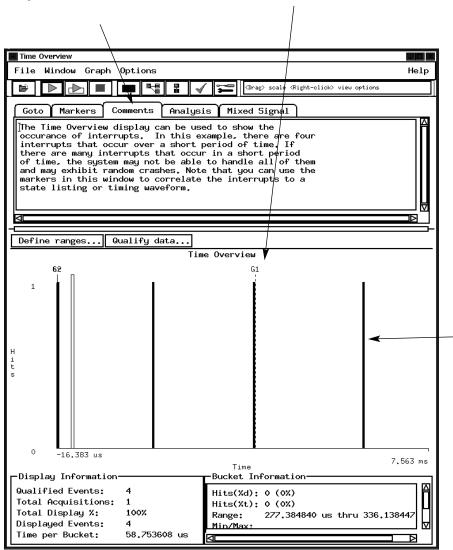

| Post-Processing Analysis Tools                                                                                                                             | Rapidly consolidate large amounts of data into displays that provide insight into your system's behavior.<br>(See page 34)                                                                                                                                                   |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

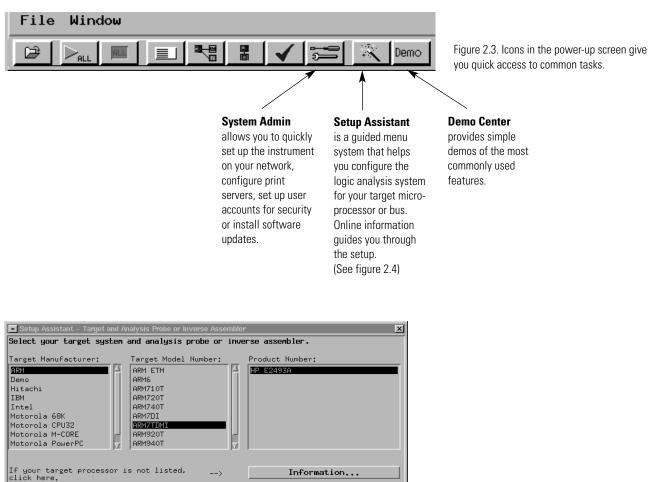

| Setup Assistant                                                                                                                                            | Quickly configure the logic analysis system for your target microprocessor. (See page 9)                                                                                                                                                                                     |  |

| Tabbed Interface                                                                                                                                           | <ul> <li>Groups like tasks together so you can quickly find and complete the task you want to perform.</li> <li>Spend your time solving problems, not setting up a measurement.</li> </ul>                                                                                   |  |

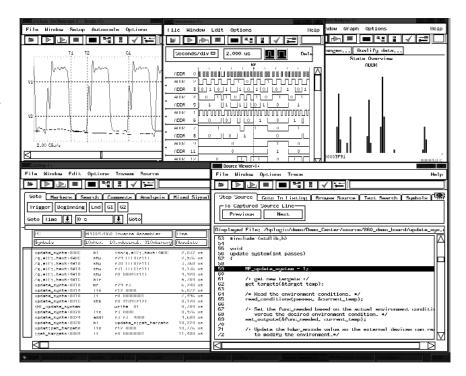

| Multi-Windowed View of<br>Target System Activity                                                                                                           | <ul> <li>View your cross-domain measurements, time-corrected on the same screen. (See page 10)</li> <li>Debug faster because you can view system activity at a glance.</li> </ul>                                                                                            |  |

| Global Markers                                                                                                                                             | Track a symptom in one domain (e.g., timing) to its cause in another domain (e.g., analog).                                                                                                                                                                                  |  |

| Resizable Windows and Data Views                                                                                                                           | <ul> <li>Magnify your view or zoom in on a boxed area of interest.</li> <li>Resize waveforms and data or quickly change colors to highlight areas of interest.</li> </ul>                                                                                                    |  |

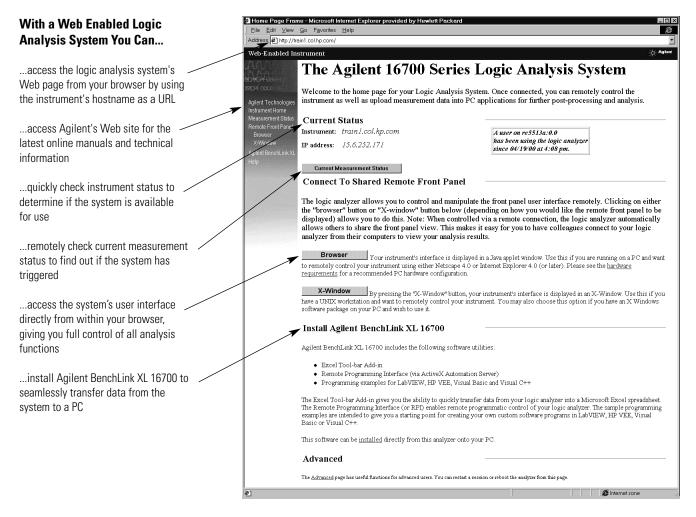

| Web-Enabled System                                                                                                                                         | <ul> <li>Directly access the instrument's web page from your web browser. (See page 11)</li> <li>Remotely check the instrument's measurement status without disturbing the acquisition.</li> <li>Remotely access, monitor and control your logic analysis system.</li> </ul> |  |

| Network Security         • Protect your networked assets and comply with your company's security requirements with i logins that provide system integrity. |                                                                                                                                                                                                                                                                              |  |

### System Overview Selecting the Right System

#### Selecting a system for your application

#### Select a mainframe (page 7)

Choose a system based on your needs:

- Self-contained unit or a unit with

- external mouse, keyboard, and monitorExpander frame for large channel count requirements

#### Determine your probing requirements (page 13)

- Are you analyzing a microprocessor?

- Do you need to probe a specific package type?

# Select the measurement modules to meet your application needs

- State/Timing Logic Analyzers (page 16)

- Oscilloscopes (page 25)

- Pattern Generation (page 28)

- Emulation (page 32)

# Add post-processing tool sets for analysis and insight (page 34)

- Source correlation

- Data communications

- System performance analysis

- Serial analysis

- Tool development kit

#### Support, services, and assistance (page 111)

- Training classes

- Consulting

- On-line support

- Warranty extension

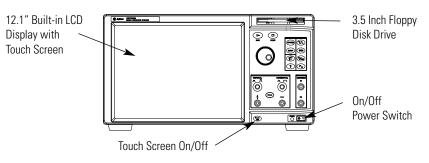

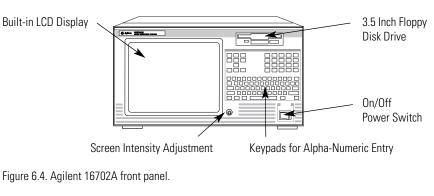

### **Mainframes** Display

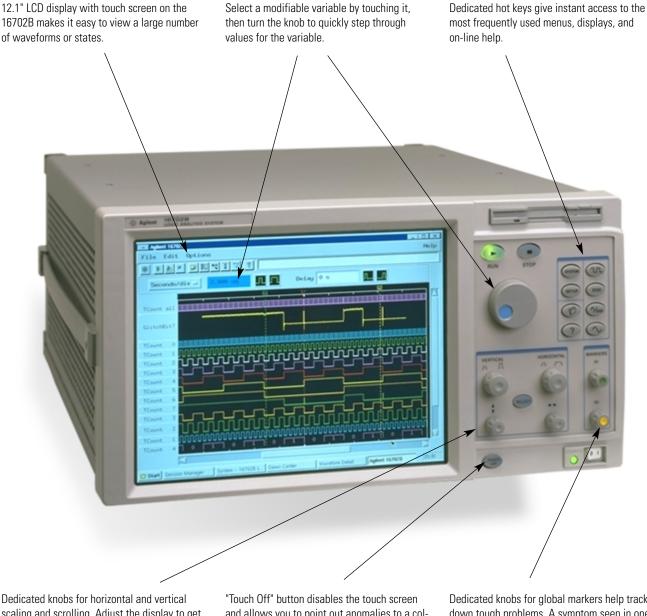

Dedicated knobs for horizontal and vertical scaling and scrolling. Adjust the display to get just the information you need to solve your problem.

and allows you to point out anomalies to a colleague without altering the display settings.

Dedicated knobs for global markers help track down tough problems. A symptom seen in one domain (e.g., timing) can be tied to its cause in another domain (e.g., analog).

Figure 2.1. The Agilent 16702B quickly tracks down problems in your design while saving precious bench space.

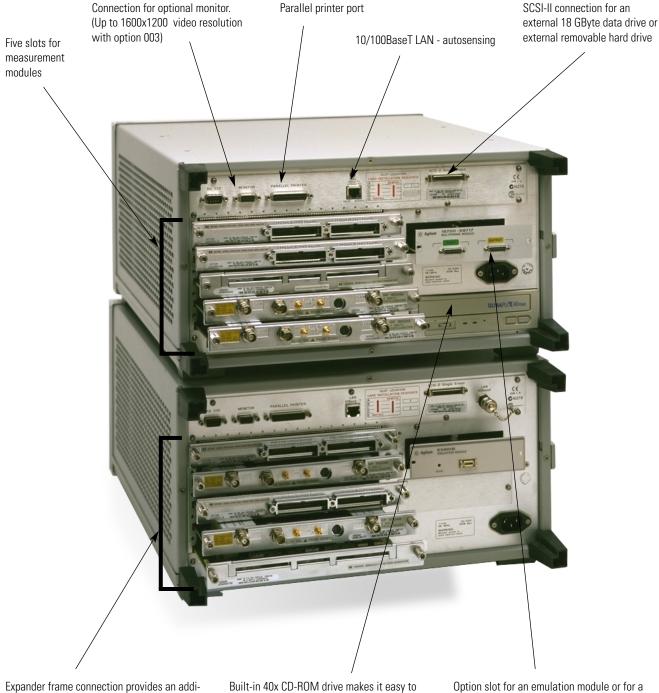

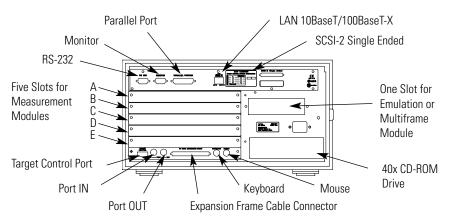

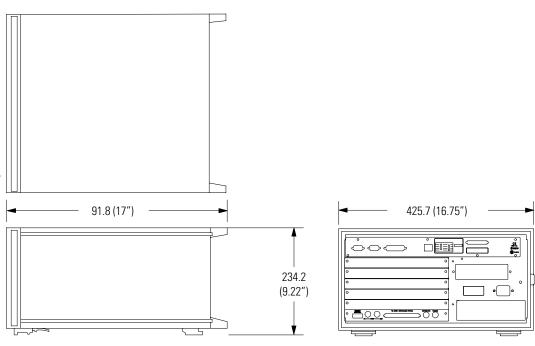

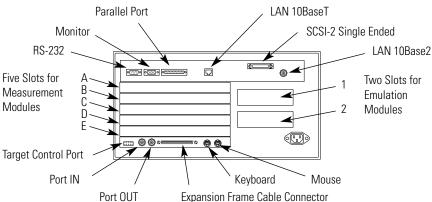

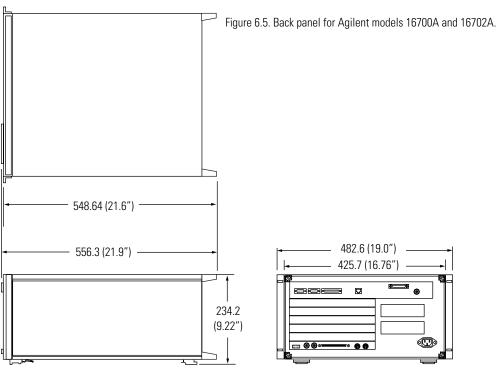

### Mainframes Back Panel

Expander frame connection provides an additional five slots for measurement modules. Built-in 40x CD-ROM drive makes it easy to install or update system software, processor support, or tool sets.

Option slot for an emulation module or for a multiframe module. Multiframe option allows up to eight mainframes and expanders to be combined so that you can see all the buses in a complex target system.

Figure 2.2. The mainframe and expander frame provide advanced capabilities for debugging complex target systems.

### Mainframes System Screens

Cancel Help Summary... Component ID...

<-- Prev Next

--->

Figure 2.4. Setup Assistant gets you up and running quickly.

### Mainframes System Screens

#### See the Big Picture of Your Prototype System's Behavior

A large external display (option 001) with multiple, resizable windows allows you to see at a glance more of your target system's operation. A builtin, flat-panel display in the 16702B fits in environments with limited space. Color lets you highlight critical information so you can find it quickly.

Use one system to examine target operation from different perspectives. Multiple time-correlated views of data let you confirm both signal integrity and software execution flow. These views are invaluable in solving crossdomain problems.

Figure 2.5. You can quickly isolate the root cause of system problems by examining target operation across a wide analysis domain, from signals to source code.

### Mainframes System Screens

#### Expanding Possibilities with Network Connectivity

Web-enabled instrumentation gives you the freedom to access the system—anywhere, anytime. Have you ever needed to check on a measurement's status while you were in a remote location? Now you can.

Figure 2.6. Your logic analyzer is its own web site. From the Home Page, you can perform multiple remote functions.

### Mainframes BenchLink XL

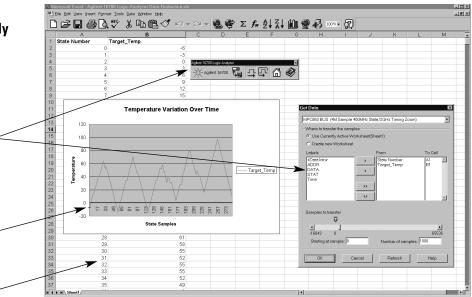

#### Agilent BenchLink XL 16700 Moves Your Data Automatically into Microsoft<sup>®</sup> Excel for Advanced Offline Analysis

BenchLink XL is shipped with each logic analysis system and can be downloaded to your PC from the system's own web page. Use the Agilent BenchLink XL tool bar to connect to a logic analysis system. Select from the available labels and specify the destination cell location in Microsoft Excel.

Use Microsoft Excel's powerful functions to post-process captured trace data for the insight you need.

Import data from a current acquisition or data previously saved to a file via the File Out tool.

Figure 2.7. Transfer data into Microsoft Excel with just a click of the mouse.

#### Programming

BenchLink XL 16700 also includes an Active-X automation server to provide programmatic control of the logic analysis system from an external environment, such as LabVIEW or the Microsoft VisualStudio environment of Visual Basic and Visual C++ tools. The instrument's Remote Programming Interface (or RPI) also allows you to write Perl or other scripts to control the logic analyzer. Use the sample programs provided to assist you in creating your own custom programs.

### **Probing Solutions** Criteria for Selection

#### Why is Probing Important?

Your debugging tools perform three important tasks: probing your target system, acquiring data, and analyzing data. Data acquisition and analysis tools are only as effective as the physical interface to your target system. Use the following criteria to see how your probing measures up.

#### How to Determine Your Requirements

To determine what probing method is best to use you need to take the following into consideration:

- The number of signals to be probed

- The ability to design probing connectors on the target PC board itself

- Mechanical probing clearance requirements

- Signal loading effects

- Ease of attachment

- Package type to be probed Dual In-line Package DIP PGA Pin Grid Array BGA Ball Grid Array PLCC Plastic Leaded Chip Carrier PQFP Plastic Quad Flat Pack TQFP Thin Quad Flat Pack SOP Small Outline Package TSOP Thin Small Outline Package

- Package Pin Pitch (distance between pin centers)

Figure 3.1. A rugged connection lets you focus on debugging your target, not your probe.

| Immunity to Noise | EMF noise is everywhere and can corrupt your data. Active<br>attenuator probing can be particularly susceptible to noise effects.<br>Agilent Technologies designs probing solutions with high immunity to<br>transient noise.                                                           |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Impedance         | High input impedance will minimize the effect of probing on your circuit. Although many probes are acceptable for lower frequencies, capacitive loading becomes very significant at higher frequencies.                                                                                 |

| Ruggedness        | A flimsy probe will give you unintended open circuits. Agilent<br>Technologies' probes are mechanically designed to relieve strain and<br>ensure a rugged and reliable connection.                                                                                                      |

| Connectivity      | A multitude of device packages exist in the digital electronics industry.<br>Check our large selection of probing solutions designed for specific<br>chip packages or buses. As an alternative, we offer reliable<br>termination adapters that work with standard on-target connectors. |

### Probing Solutions Technologies

#### Choosing the Technique that Best Fits Your Application

Agilent Technologies provides a wider variety of probing solutions than anyone else in the industry. Each offers advantages for particular situations. We like to think of our probe technology as helping you get your signals off to a great start.

|                                                                  | Probing Alternative                                     | Advantages                                                                                                                                                                                                | Limitations                                                         |

|------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Figure 3.2.<br>Surface mount IC clips                            | General-purpose lead sets<br>and surface mount IC clips | Most flexible method.<br>Works in conjunction with<br>SMD clips and Wedge<br>adapters. Included with<br>logic analyzer purchase.                                                                          | Can be cumbersome when<br>connecting a large number of<br>channels. |

| Figure 3.3. General-purpose probing solution                     |                                                         |                                                                                                                                                                                                           |                                                                     |

| Figure 3.4.<br>Ultra-fine pitch<br>surface mount<br>device clips | Ultra-fine pitch surface<br>mount device clips          | Smallest IC clips in the<br>industry to date (down to<br>0.5 mm). Work with both<br>logic analyzer and scope<br>probing systems.                                                                          | Same as above plus small incremental cost.                          |

| Figure 3.5.<br>Agilent Wedge Probe<br>Adapters for QFP package   | Wedge probe adapter<br>for QFP packages                 | Compressible dual<br>conductors between<br>adjacent IC legs make 3-16<br>adjacent signal leads<br>available to logic analyzer<br>and scope probing systems.                                               | Same as above plus small incremental cost.                          |

| Figure 3.6.<br>Elastomeric<br>probing solution                   | Elastomeric solutions for<br>generic QFP packages       | Provide access to all signal<br>leads for generic ΩFP<br>packages [including custom<br>ICs). Uses a combination of<br>one probe adapter and four<br>flexible adapters, plus<br>general-purpose lead sets. | Requires minimal keep out area.<br>Moderate incremental cost.       |

| $\sim$                                                           |                                                         |                                                                                                                                                                                                           |                                                                     |

# **Probing Solutions** Technologies

|           |                                                                                     | Probing Alternative                                                | Advantages                                                                                                                                                                                                                                                                                                         | Limitations                                                                                                                                    |

|-----------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Figure 3.7. Normal-density direct connection solution                               | Direct connection to<br>device under test (built-in<br>connectors) | Very reliable and<br>convenient probing system<br>when frequent probing<br>connections are required<br>(for manufacturing or for<br>field tests). Connectors can<br>be located at optimal<br>positions in the device<br>under test. Can work in<br>conjunction with Agilent<br>Technologies inverse<br>assemblers. | Requires advance planning to<br>integrate into design process.<br>Moderate incremental cost.                                                   |

|           | Figure 3.8.<br>High-density direct<br>connection solution                           |                                                                    |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                |

|           |                                                                                     | Analysis probes for<br>specific processors and<br>buses            | Support for over 200<br>different processors and<br>buses. Includes reliable<br>logic analyzer probe pod<br>connectors, logic analyzer<br>configuration files and<br>device-specific inverse<br>assemblers.                                                                                                        | May require moderate clearance<br>around processor or bus.<br>Moderate to significant extra<br>cost depending on specific<br>processor or bus. |

|           |                                                                                     | Custom probing adapters                                            | Custom probing solution<br>designed to meet the<br>requirements of your<br>specific processors,                                                                                                                                                                                                                    | Can be costly. May require a long lead time.                                                                                                   |

|           | locument "Probing Solutions                                                         |                                                                    | buses, DSPs, or<br>programmable devices.                                                                                                                                                                                                                                                                           |                                                                                                                                                |

| for Agile | locument "Probing Solutions<br>nt Technologies Logic<br>Systems," publication numbe | r                                                                  |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                |

Analysis Systems," publication numbers 5968-4632E, for more information on probing related issues.

# Selecting the Correct Modules to Meet Your Needs

Selecting the proper logic analyzer modules for your needs requires a series of choices concerning performance, cost, and the amount of data you will be able to capture. The following table explains these factors in greater detail.

#### **Considerations for Choosing Modules**

| Microprocessor/<br>Bus Support | Will you be using an analysis probe for a particular processor or bus? If so, a good starting point is the document <i>Processor</i> and Bus Support for Agilent Technologies Logic Analyzers, publication number 5966-4365E, available on the worldwide web at www.agilent.com/find/logicanalyzer. This document provides the number of channels and state speed required for any particular analysis probe. It also indicates which analysis modules are supported and how many are required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| State Speed                    | <ul> <li>State analysis uses a clock or strobe signal from your system under test to determine when to sample. Because state analysis samples are synchronous with the system under test, they provide a view of how your system is executing. You can use state analysis to capture bus cycles from a microprocessor or I/O bus and convert the data into processor mnemonics or bus transactions using an Agilent Technologies inverse assembler.</li> <li>Select a state acquisition system that provides the speed and headroom you need without breaking your budget. Remember that a microprocessor will have an internal core frequency that is normally 2X-5X the speed of the external bus.</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |

| Headroom                       | You may realize a better return on your investment if you consider possible future needs when purchasing analysis modules.<br>The things to consider are primarily state speed and memory depth.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Setup/Hold                     | <ul> <li>Logic analyzers require time for the data at the inputs to become valid (setup time), and time to capture the data (hold time). A lengthy setup and hold can make the difference between capturing valid data or data in transition.</li> <li>Your device under test will ensure that data is valid on the bus for a defined length of time. This is known as the data valid window. Your target's data valid window must be large enough to meet the setup/hold specifications of the logic analyzer. The data valid window of most devices is generally less than half of the clock period. Don't be fooled by "typical" setup and hold specifications for logic analyzers.</li> <li>As bus speeds increase, the time window during which data is stable decreases. Jitter, skew, and pattern-dependent ISI add more uncertainty and consume a greater portion of the data-valid window at high speeds. A logic analyzer with adjustable setup/hold with fine position resolution provides unparalleled measurement accuracy at high frequencies.</li> </ul> |

| Timing Resolution              | Timing analysis uses the logic analyzer's internal clock to determine when to sample. Since timing analysis samples asynchronously to the system under test, you should consider what accuracy you will need to verify your system. Accuracy is made up of two elements: sample speed and channel-to-channel skew. Remember to evaluate both of these elements and be careful of logic analyzers that have a fast sample speed with a large channel-to-channel skew.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Transitional Timing            | If your system has bursts of activity followed by times with little activity, you can use transitional timing to capture a longer trace. In transitional timing, the analyzer samples data at regular intervals, but only stores the data when there is a transition on one of the signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Channel Count         | Determine the number of signals you want to analyze on your system under test. You will need this number of channels in<br>your logic analyzer. Even if you have enough channels to view all the signals in your system today, you should consider logic<br>analysis systems that allow you to add more channels for your future application needs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Depth          | <ul> <li>Complex architectures and bus protocols make your debugging job increasingly challenging. Split transactions, multiple outstanding transactions, pipelining, out-of-order execution, and deep FIFOs, all mean that the flow of data related to a problem can be distributed over thousands or millions of bus cycles.</li> <li>The keys to useful insight are the combination of deep memory with responsive display refresh, search, rescaling, and scrolling to help you find information and answers quickly. Hardware-assisted memory management in the Agilent 16718A, 16719A, 16750A, 16751A, and 16752A state and timing analysis modules makes quick work of refreshing the display, rescaling, scrolling, and searching. It takes only a few seconds to refresh, rescale, or scroll a 32M sample record. Agilent Technologies offers a range of state and timing analyzer modules with memory depths up to 32M samples, at prices to meet your budget.</li> </ul> |

| Triggering            | <ul> <li>The logic analyzer memory system is similar to a circular buffer. When the acquisition is started, the analyzer continuously gathers data samples and stores them in memory. When memory becomes full, it simply wraps around and stores each new sample in the place of the sample that has been in memory the longest. This process will continue until the logic analyzer finds the trigger point. The logic analyzer trigger stops the acquisition at the point you specify and provides a view into the system under test. The primary responsibility of the trigger is to stop the acquisition, but it can also be used to control the selective storage of data. Consider a logic analyzer with the trigger resources you need to quickly set up your measurements.</li> <li>After memory depth, triggering is the most important aspect of a logic analyzer to consider. On the one hand, powerful</li> </ul>                                                      |

|                       | triggering resources and algorithms will allow you to focus on potential problem sources without using up valuable memory.<br>On the other hand, to be useful, the trigger must be easy to set up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Other<br>Measurements | In addition to the measurements made with an analysis probe, consider whether you need to monitor other signals. Be sure to allow enough channels to make those measurements. For state measurements, the state speed of the analyzer must be at least as high as the clock speed of your circuit. You may want to test the margin in your circuit by operating it at higher than the nominal clock speed to determine if the analyzer has sufficient clock speed. For timing measurements, the timing analyzer rate should be from 2-10X the clock speed of your target.                                                                                                                                                                                                                                                                                                                                                                                                           |

#### **Considerations for Choosing Modules (continued)**

# Key Features of Agilent's State/Timing Modules

- Memory depth up to 32M samples at a price to meet your budget

- State analysis up to 400 MHz

- Timing analysis up to 4 GHz

- VisiTrigger combines powerful functionality with an intuitive user interface

- Timing Zoom 2-GHz timing on all channels

- Eye finder for automatic setup and hold on all channels

| Triggering for the<br>most elusive<br>problems     | VisiTrigger combines powerful trigger functionality with a user interface<br>that is easy to understand and use. Capturing complex sequences of<br>events is as simple as pointing to the function you want to use and filling in<br>the blanks to customize it to your specific situation. |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reliable<br>measurements<br>on high-speed<br>buses | Eye finder automatically adjusts the setup and hold on every channel,<br>eliminating the need for manual adjustment and ensuring the highest<br>confidence in accurate state measurements on high-speed buses.                                                                              |

| High-speed<br>timing on<br>all channels            | Timing Zoom provides the data acquisition speed you need for high-speed microprocessors and buses.                                                                                                                                                                                          |

#### Choose the Logic Analyzer and Measurement Modules that Best Fit Your Application

| State/Timing<br>Modules | General-<br>purpose<br>hardware<br>debug | 8/16 Bit<br>processor<br>debug | 32/64 Bit<br>processor<br>debug or<br>channel<br>intensive<br>systems | High-<br>speed<br>bus<br>analysis | Timing<br>margin<br>analysis or<br>characterize<br>setup/hold | Deep trace<br>capture<br>with timing<br>or state<br>analysis | High-<br>speed<br>computer<br>debug | Analysis of<br>data intensive<br>systems and<br>performance |

|-------------------------|------------------------------------------|--------------------------------|-----------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------|

| 16710A                  | $\checkmark$                             | $\checkmark$                   |                                                                       |                                   |                                                               |                                                              |                                     |                                                             |

| 16711A                  | $\checkmark$                             | $\checkmark$                   |                                                                       |                                   |                                                               |                                                              |                                     |                                                             |

| 16712A                  | $\checkmark$                             | $\checkmark$                   |                                                                       |                                   |                                                               |                                                              |                                     |                                                             |

| 16715A                  |                                          |                                | $\checkmark$                                                          |                                   |                                                               | $\checkmark$                                                 | $\checkmark$                        |                                                             |

| 16716A                  | $\checkmark$                             | $\checkmark$                   | $\checkmark$                                                          |                                   | $\checkmark$                                                  |                                                              | $\checkmark$                        |                                                             |

| 16717A                  |                                          |                                | $\checkmark$                                                          | $\checkmark$                      | $\checkmark$                                                  | $\checkmark$                                                 | $\checkmark$                        |                                                             |

| 16718A                  |                                          |                                | $\checkmark$                                                          | $\checkmark$                      | $\checkmark$                                                  | $\checkmark$                                                 | $\checkmark$                        |                                                             |

| 16719A                  |                                          |                                | $\checkmark$                                                          | $\checkmark$                      | $\checkmark$                                                  | $\checkmark$                                                 | $\checkmark$                        |                                                             |

| 16750A                  |                                          |                                | $\checkmark$                                                          | $\checkmark$                      | $\checkmark$                                                  | $\checkmark$                                                 | $\checkmark$                        |                                                             |

| 16751A                  |                                          |                                | $\checkmark$                                                          | $\checkmark$                      | $\checkmark$                                                  | $\checkmark$                                                 | $\checkmark$                        |                                                             |

| 16752A                  |                                          |                                | $\checkmark$                                                          | $\checkmark$                      | $\checkmark$                                                  | $\checkmark$                                                 | $\checkmark$                        |                                                             |

| 16517/18A               |                                          |                                |                                                                       | $\checkmark$                      | $\checkmark$                                                  |                                                              |                                     |                                                             |

A variety of measurement modules allow you to select the optimum combination of performance, features, and price to meet your specific needs now and in the future.

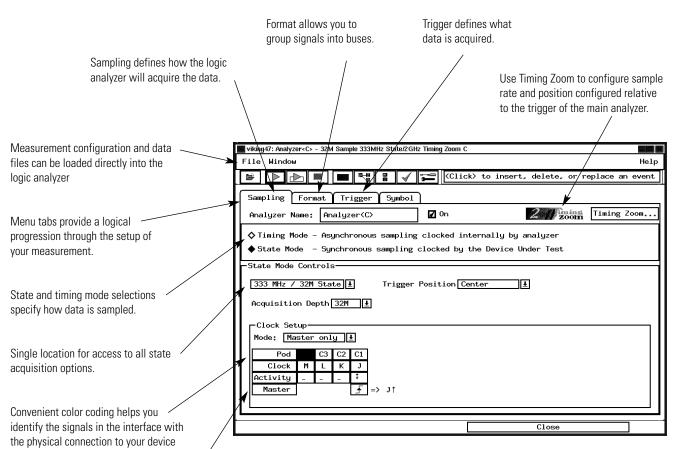

#### Improve Your Productivity with an Intuitive User Interface

Agilent Technologies has made the user interface easy to understand and use. Now you can spend more time making measurements and less time setting up the logic analyzer.

Figure 4.1. Setting up your logic analyzer has never been this easy.

Clocking for state measurements can be quickly defined using the clock setup menu.

under test.

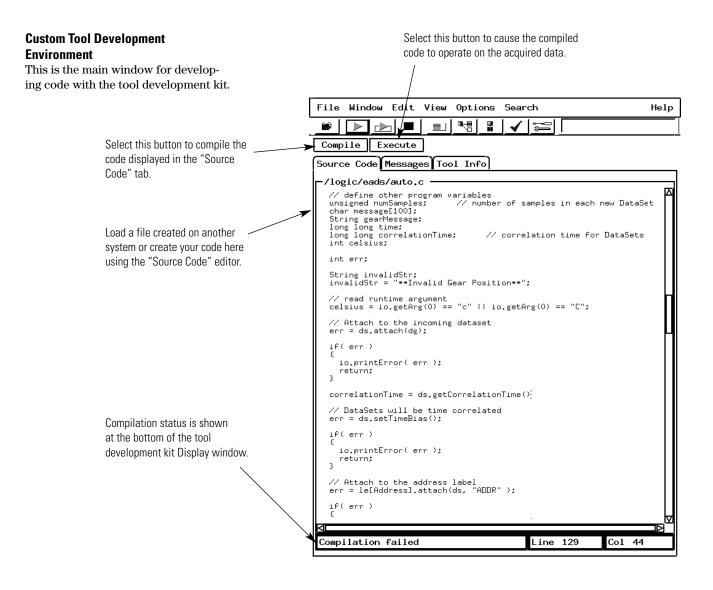

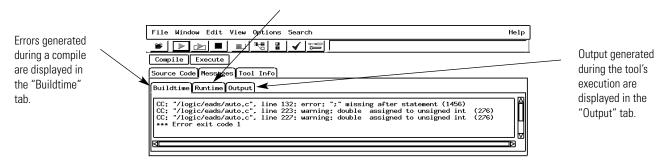

#### VisiTrigger Quickly Locates Your Most Elusive Problems

VisiTrigger technology is a breakthrough in logic analysis usability. It combines increased trigger functionality with a user interface that is easy to understand and use. Now with VisiTrigger, capturing complex events is as simple as pointing to the trigger function and filling-in-the-blanks.

#### **Features and Applications**

| VisiTrigger<br>(available in the 16715A,<br>16716A, 16717A, 16718A, | <ul> <li>Use graphical views and sentence-like structures to help you<br/>define a trace event.</li> <li>Select trigger functions as individual trigger conditions or as</li> </ul>                                                                     |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16719A, 16750A, 16751A,<br>and 16752A state/timing<br>modules)      | <ul> <li>building blocks to easily customize a trigger for your specific task.</li> <li>Set global counters to count events such as the number of times a function executes, or the number of accesses to an I/O port.</li> </ul>                       |

|                                                                     | <ul> <li>Set, clear or evaluate flags by any module in the frame. Flags allow<br/>you to set up a trigger that is dependent on activity from more than<br/>one bus in the system.</li> <li>Specify four way activity IE/THEN/ELSE branching.</li> </ul> |

Specify four-way arbitrary IF/THEN/ELSE branching.

#### Examples of Problems that Can be Captured Easily with VisiTrigger

| Description                                                              | Typical Applications                                                                                                                                                                     | Graphic                                                              |  |  |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| Pulse too narrow or too wide                                             | <ul> <li>Line hangs at wrong level (high or low).</li> <li>Asynchronous input (for example, an interrupt) persists too long.</li> <li>Strobe width is too narrow or too wide.</li> </ul> | ⊢ Min width ⊣ ⊢ Max width ⊣<br>OR<br>Pulse too narrow Pulse too wide |  |  |

| Time between two edges is<br>longer than specified                       | <ul> <li>Excessive delay in responding to a bus grant request.</li> <li>Excessive delay in responding to a data valid with a data acknowledged.</li> </ul>                               | edge 1 edge 2                                                        |  |  |

| Pattern lasts longer than a specified time                               | A bus hangs up at a given value.                                                                                                                                                         | pattern                                                              |  |  |

| Pattern two exists within a specified time after pattern one is detected | <ul> <li>An incorrect response to a read or write.</li> <li>An incorrect output from a FIFO or bridge.</li> </ul>                                                                        | pattern 1                                                            |  |  |

| A pattern exists for less<br>than a specified time                       | • A driver is not holding a bus value long enough for a receiver to respond.                                                                                                             | pattern time                                                         |  |  |

Your most commonly used triggers are just a mouse click away with the built-in trigger functions. VisiTrigger's graphical representation shows you how the trigger condition will be defined. You can use trigger functions as building blocks to easily customize a trigger for your specific task.

Sequence levels allow you to develop a sequence of analyzer instructions to specify a trigger point or to qualify data and store only the information that interests you. Each step in the sequence contains an "IF/THEN/ELSE" structure that can evaluate up to four logic events. Each event can specify a combination of actions such as: store sample, increment counters, reset timers, trigger, or go to another step in the sequence level.

Ranges provide a way to monitor program and data accesses within a specified area in memory.

Global counters can count events such as the number of times a function executes or accesses an I/O port.

Timers can be set up to evaluate when one event happens too late or too soon with respect to another event.

In timing mode, edge terms let you trigger on a rising edge, falling edge, either edge, or a glitch.

Patterns and their logical combinations let you identify which states to store, when to branch and when to trigger.

View current information on the state of the timers, counters, flags, and the trigger sequence level.

Save and recall up to ten of your custom trigger setups without loading a new configuration file.

|                                                                         | /                       |     |

|-------------------------------------------------------------------------|-------------------------|-----|

| MPC860 BUS - 333MHz State/2GHz Timing Zoom 2M St                        | ample C                 |     |

| File Window Edit Options Clear                                          |                         | Hel |

|                                                                         |                         |     |

|                                                                         |                         |     |

| Sampling Format Trigger Symbol                                          | ₩                       |     |

| Trigger Functions Settings Overview Statu                               | s Save/Recall           |     |

| General Timing                                                          | Trigger function librar | ies |

| Find pattern                                                            | pattern                 | _   |

| Find edge                                                               | pattern                 | _   |

| Find edge AND pattern<br>Find width violation on pattern/pulse          |                         |     |

| Find width violation on pattern/pulse<br>Find Nth occurrence of an edge | edge                    |     |

| Find with occurrence of an edge                                         | Z Cage                  |     |

|                                                                         |                         |     |

| Replace Insert before                                                   | Insert after Delete     |     |

|                                                                         |                         |     |

| Trigger Sequence                                                        |                         |     |

|                                                                         | Laura Annal             |     |

| If ADDR In range 00000044 000042A9 H<br>DATA = XXXX03E7 Hex             | tex And                 |     |

| occurs 1 time                                                           |                         |     |

| then Counter 1 Increment                                                |                         |     |

| Goto 3<br>Else if ADDR > 000042A9 Hex                                   |                         |     |

| then Timer 1 Start from reset                                           |                         |     |

| 🖌 Goto Next                                                             |                         |     |

| Else if ADDR < 00000044 Hex<br>then Goto 1                              |                         |     |

|                                                                         |                         |     |

| 2 FIND EDGE AND PATTERN                                                 |                         |     |

|                                                                         |                         |     |

| Find *TS Edge                                                           |                         |     |

|                                                                         |                         |     |

| and ADDR = XXXX43C5 Hex                                                 |                         |     |

| then Flag 1 Set                                                         |                         |     |

| then Flag 1 Set                                                         |                         |     |

| Trigger and fill memory                                                 |                         |     |

|                                                                         |                         |     |

|                                                                         |                         |     |

| Help                                                                    | Close                   |     |

|                                                                         |                         |     |

|                                                                         | <b>\</b>                |     |

| 1                                                                       | $\mathbf{X}$            |     |

| /                                                                       | `                       |     |

Flags can be set, cleared and evaluated by any 16715A/16A/17A/18A/19A/50A/51A/52A module in the frame. This allows you to set up a trigger that is dependent on activity from more than one bus in the system.

Values can be easily entered directly into the trigger description.

Figure 4.2. Set up your trigger in terms of the measurements you want to make.

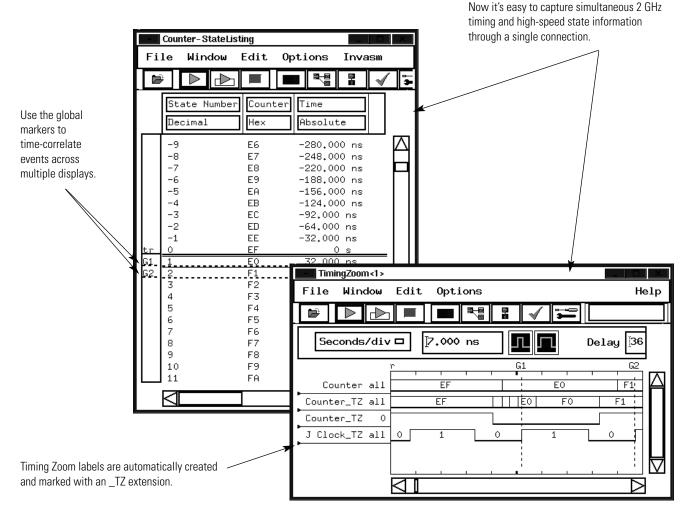

#### 2 GHz Timing Zoom Provides High-Speed Timing Analysis Across All Channels, All the Time

When you're pushing the speed envelope, you may run into elusive hardware problems. Capturing glitches and verifying that your design meets critical setup/hold times can be difficult without the proper tools. With Timing Zoom you have access to the industry's most powerful tool for high-speed digital debug.

#### **Features and Applications**

Timing Zoom (available in the 16716A, 16717A, 16718A, 16719A, 16750A, 16751A, and 16752A state/timing modules)

- Simultaneously acquire up to 16K of data at 2 GHz timing and 400 MHz state across all channels, all the time, through the same connection

- Vary the Timing Zoom sample rate from 250 MHz to 2 GHz

- Vary the placement of Timing Zoom data around the trigger point

- Efficiently characterize hardware with 500 ps resolution

Figure 4.3. Verifying critical edge timing in your system is easy with Agilent Technologies' 2 GHz Timing Zoom technology.

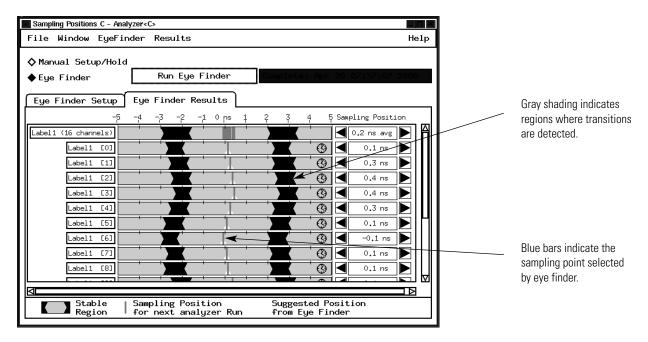

#### **Eye Finder**

Agilent's eye finder examines the signals coming from the circuit under test and automatically adjusts the logic analyzer's setup and hold window on each channel. Eye finder, combined with 100 ps adjustment resolution on Agilent's logic analyzer modules, yields the highest confidence in accurate state measurements on high-speed buses. It takes less than a minute to run eye finder. No special setup or additional equipment is required. You only need to run eye finder once, when the logic analyzer is set up and connected to the target.

Figure 4.4. The eye finder display.

The eye finder display shows:

- Regions of transitions that were discovered on all channels selected

- The sampling point selected by eye finder

If you want to select a different sample point on any individual channel, just drag and drop the blue "sample" bar at the desired point. Times in the eye finder display are referenced to the incoming clock transitions. The center of the display (labeled "0 ns") corresponds to the clock transitions.

#### Eye Finder as an Analytical Tool

Eye finder is very useful as a first-pass screening test for data valid windows. Because eye finder quickly examines all channels, it is considerably faster than examining each channel with an oscilloscope. After running eye finder, you may want to use an oscilloscope to examine only those signals that are close to your desired specifications for setup and hold.

Eye finder also can quickly provide useful diagnostic or troubleshooting information. If a channel has an unexpectedly small data valid window, or an anomalous offset relative to clock, this could be an indication of a problem, or could be used to validate the cause of an intermittent timing problem.

Differences in the position of the stable region from one signal to another on a bus indicate skew. An indication of excessive skew on eye finder can help isolate which channels you want to check with an oscilloscope, or with the Timing Zoom 2 GHz timing analysis mode in your logic analyzer.

#### When Do You Need Eye Finder?

Eye finder becomes critical when the data valid window is <2.5 ns. If you're unsure where your clock edge is relative to the data valid window, you can run eye finder for maximum confidence. If the clock in your system runs at 100 MHz or slower, and the clock transitions are approximately centered in the data valid window, you may not see any transition zones indicated in the eye finder display. This is because eye finder only examines a time span of 10 ns centered about the clock.

#### **Examples of When to Run Eye Finder**

You should use eye finder in the following situations:

Probing a new target, or probing different signals in the same target

• Because eye finder examines the actual signals in the circuit under test, you should run it whenever you probe a different bus or a different target.

# Significant change of target temperature

• The propagation delays and signal levels in your target system may vary with temperature. If, for example, you place your target system in a controlled temperature chamber to evaluate its operation over a range of temperatures or to troubleshoot a problem that only occurs at high or low temperatures, you should run eye finder after the target system stabilizes at the new ambient temperature.

### Data Acquisition and Stimulus Oscilloscope Modules

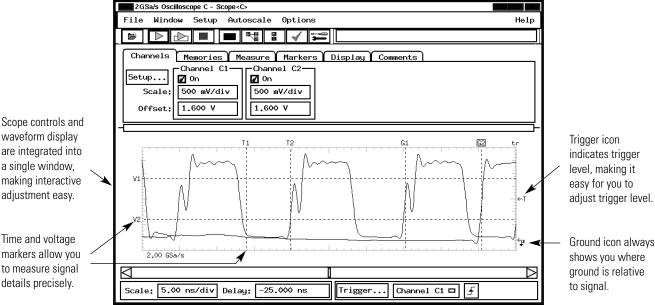

When integrated into the 16700 Series logic analysis systems, the oscilloscope modules make powerful measurement and analysis more accessible, so you can find the answers to tough debugging problems in less time. Oscilloscope controls are easy to find and use.

#### Multiple Views of Target Behavior Isolate Problems Quicker

Frequently a problem is detected in one measurement domain, while the clues to the cause of the problem are found in another. That's why the ability to view your prototype's behavior from all angles simultaneously—from software execution to analog signals—is essential for quickly gaining insight into problems. For example, using a state analyzer you may observe a failed bus cycle. A timing problem caused by a reflection on an incorrectly terminated line may be causing the bus cycle to fail. By triggering an oscilloscope from the state analyzer, you can quickly identify the cause. The ability to cross-trigger and time-correlate state, timing, and analog measurements can help you in solving these tough problems.

Figure 4.5. All primary oscilloscope control settings, including scale factors and trigger settings, are visible simultaneously.

25

### Data Acquisition and Stimulus Oscilloscope Modules

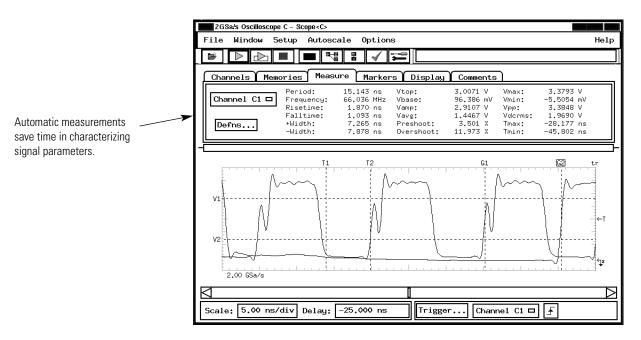

#### Automatic Measurements Quickly Characterize Signals

The Agilent Technologies 16533A and 16534A oscilloscope modules quickly characterize signals with automatic measurements of rise time, voltage, pulse width, and frequency.

# Markers Easily Set Up Timing and Voltage Margin Measurements

Four independent voltage markers and two local time markers are available to quickly set up measurements of voltage and timing margins. The global time markers of the 16700 Series logic analysis systems let you correlate state, timing, and oscilloscope measurements to track problems across multiple measurement domains.

Figure 4.6. Automatic measurements and markers let you make faster analysis.

### Data Acquisition and Stimulus Oscilloscope Modules

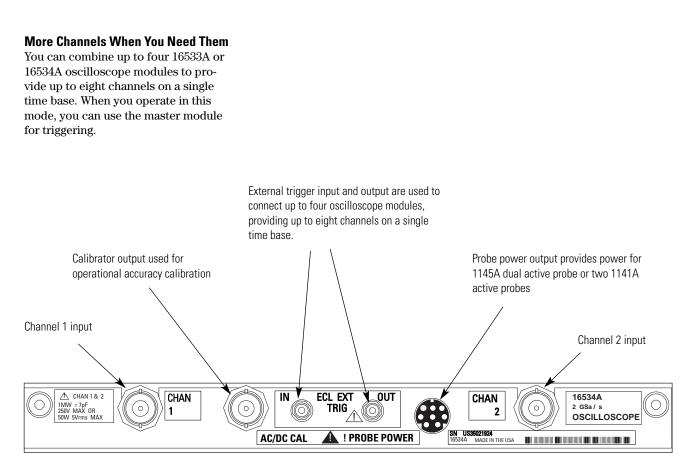

Figure 4.7. Connector panel of the 16533A and 16534A oscilloscope modules.

# Digital Stimulus and Response in a Single Instrument

Configure the logic analysis system to provide both stimulus and response in a single instrument. For example, the pattern generator can simulate a circuit initialization sequence and then signal the state or timing analyzer to begin measurements. Use the compare mode on the state analyzer to determine if the circuit or subsystem is functioning as expected. An oscilloscope module can help locate the source of timing problems or troubleshoot signal problems due to noise, ringing, overshoot, crosstalk, or simultaneous switching.

#### Parallel Testing of Subsystems Reduces Time to Market

By testing system subcomponents before they are complete, you can fix problems earlier in the development process. Use the Agilent 16522A or 16720A as a substitute for missing boards, integrated circuits (ICs), or buses instead of waiting for the missing pieces. Software engineers can create infrequently encountered test conditions and verify that their code works-before complete hardware is available. Hardware engineers can generate the patterns necessary to put their circuit in the desired state, operate the circuit at full speed or step the circuit through a series of states.

# Selecting a Pattern Generation Module

Agilent offers two different pattern generator modules for the 16700 Series logic analysis systems. If you only need a few analysis channels to do device substitution or functional testing, the 16522A is your best choice. If you need more channels of stimulus, are intent on generating stimulus using CAE tools, or require high-speed performance of up to 300 MHz, the 16720A offers unbeatable capabilities at a very affordable price.

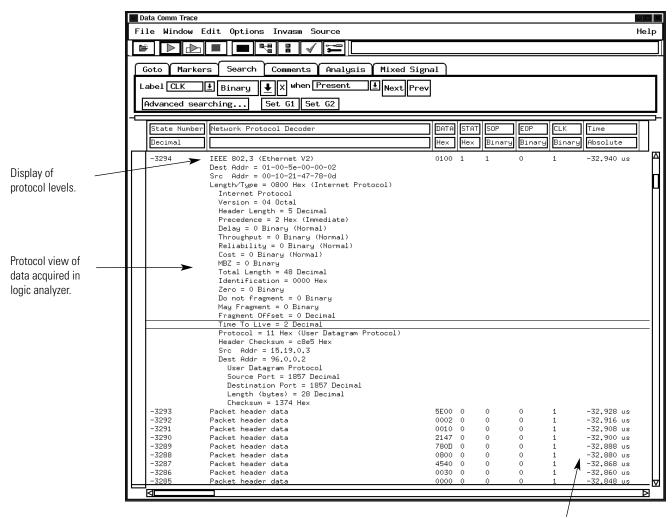

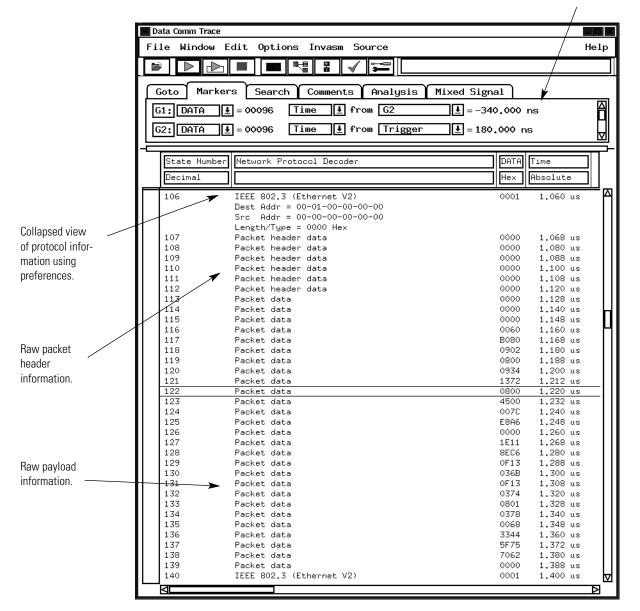

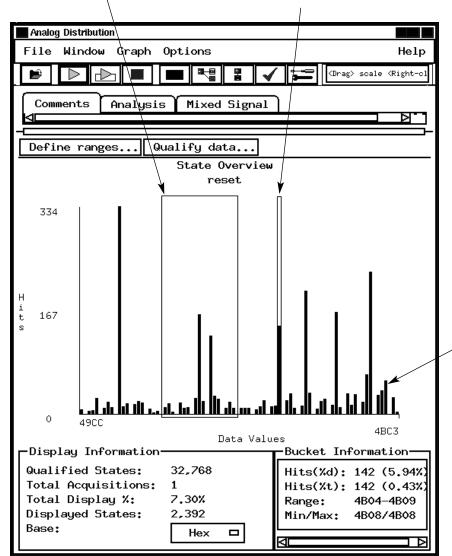

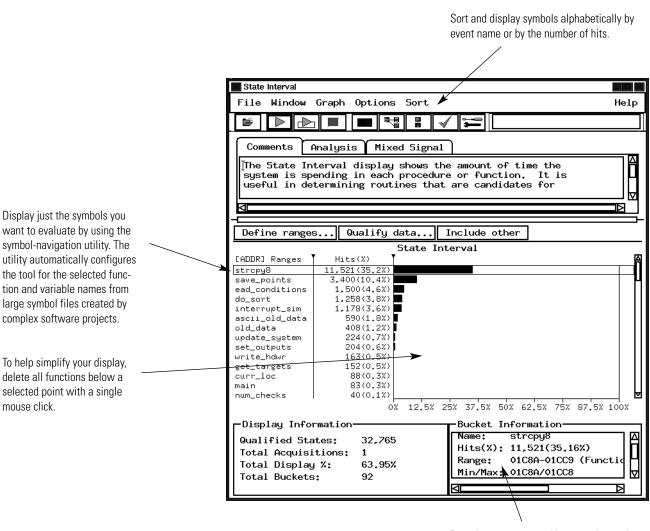

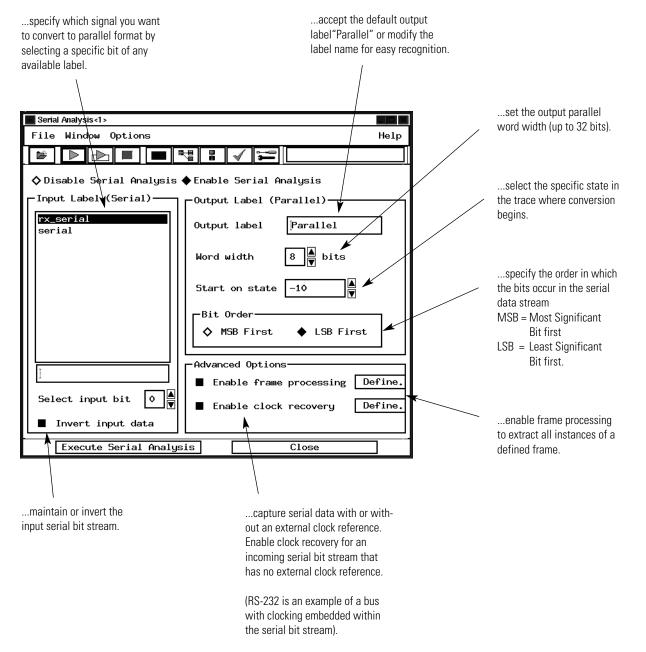

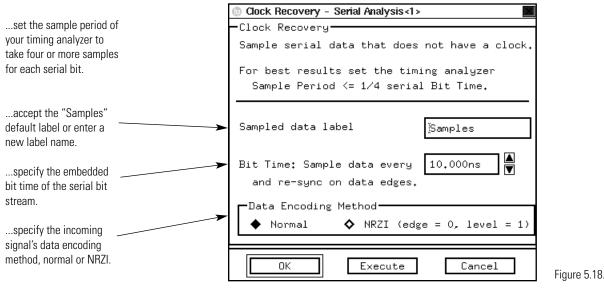

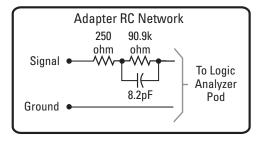

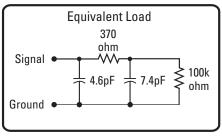

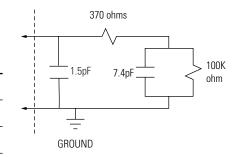

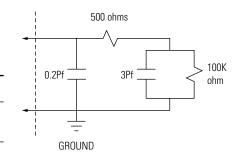

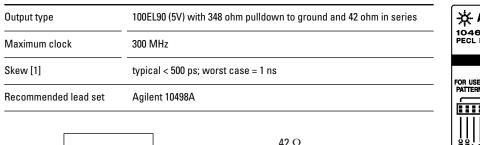

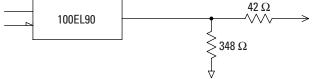

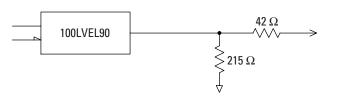

#### **Key Characteristics**